DDSをリファレンスにしたPLL-VFOの実験

※末尾にプリミックスVFOをテストした結果を追記しました。(2016-10-30)

※「PLL-VFOを使った50MHzSSBトランシーバーの製作」で実際に作り始めました。(2016-10-31)

50MHzのSSBトランシーバーを作る予定でVFOを実験中です。前回製作した7MHzトランシーバーで作り直したDDS-ICのAD9833を使用したVFOが余っているので、これを使うことを考えました。ただ、50MHzトランシーバーに必要なVFOは10MHz付近のIFを採用すると40MHz付近の周波数を出力する必要があります。AD9833の出力周波数は最大でも12.5MHzまでなのでそのままでは使用できません。

最初はミキサーICのTA7358かNE612を使用して水晶発振回路とDDSとのプリミックスVFOを考えたのですが、DDSの出力を5~10MHzとした場合に必要となるクリスタル(30~35MHz)が手持ちになかったので、別途後日実験する予定です。

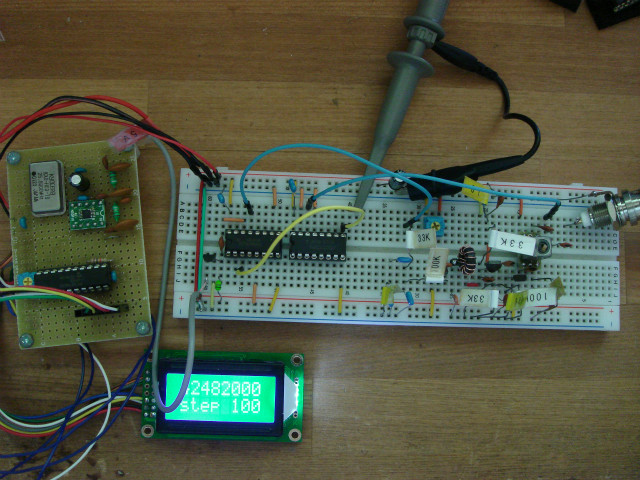

次に考えたのは、PLLを使用したVFOです。40MHz付近を発振するVCOをプリスケーラーで1/10の4MHz付近として、この周波数とAD9833で作成したリファレンスを位相比較してVCOを制御してやれば、周波数変動の少ない正確な周波数のVFOができそうです。ということでブレッドボードで実験してみました。

DDSは、周波数変更の最小ステップを10Hzとしています。プリスケーラーで1/10としているので、実際の周波数ステップは10倍の100Hz単位となります。当然、DDSを1Hzステップとすれば10Hz、0.1Hzステップとすれば1Hz単位で周波数を可変することが理論的には可能ですが、ループフィルターの設計が面倒になります。(・・と思います。←このあたりの理論はあまりよくわかっていません。)

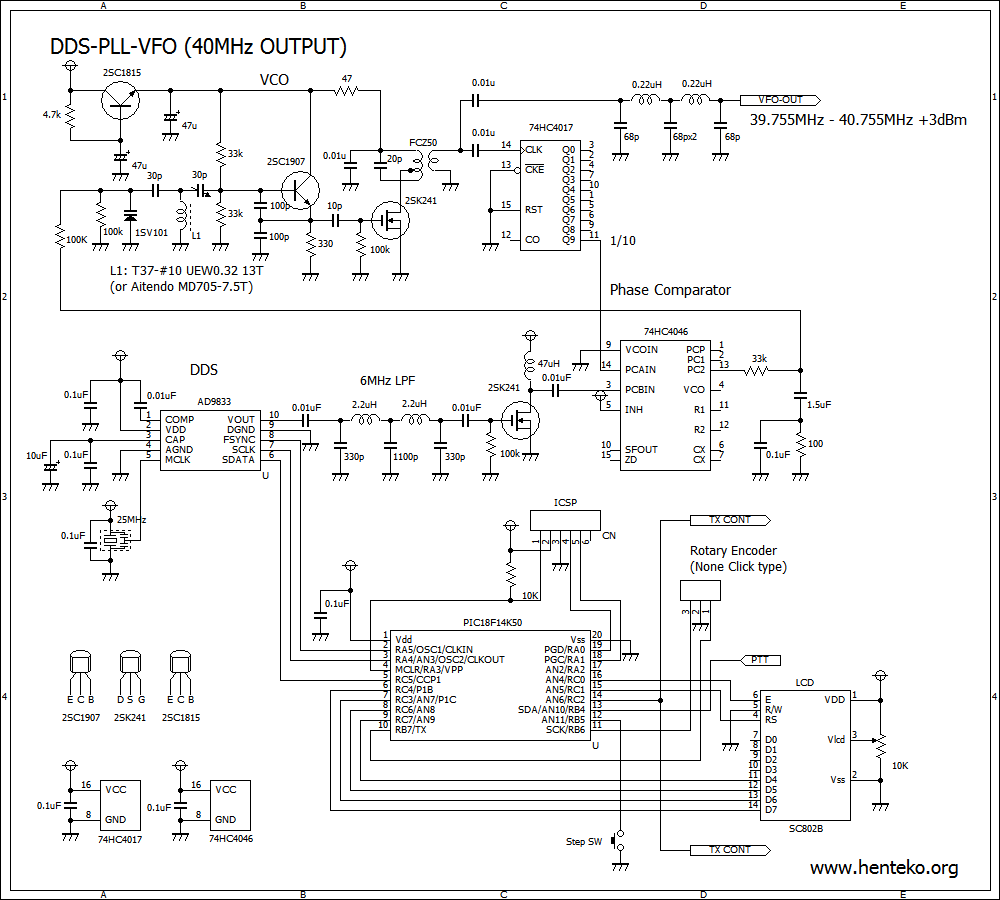

実験した回路図です。VCOは、信号純度を無視すれば39MHz~44MHz程度までは可変可能です。位相比較器は74HC4046を使用しました。最初は4046Bで実験したのですが、4MHzの位相比較はうまく動作しませんでした。DDSからの出力はそのままでは-18dBmと小さいので位相比較器の入力には弱すぎます。2SK241の広帯域アンプで増幅しました。

プリスケーラーは、計算が簡単になるように10進カウンタの74HC4017を使用しました。ロジックICは、HCタイプで最大30MHz程度までの動作速度と記憶していたので、ちょっと厳しいかな・・・と思っていましたが、手持ちの東芝製のTC74HC4017のデータシートを見てみると5Vで79MHzまで動作すると書いてあり問題ありませんでした。VCOから42.480MHzの信号を入れると1/10の4.248MHzの信号が出力されます。

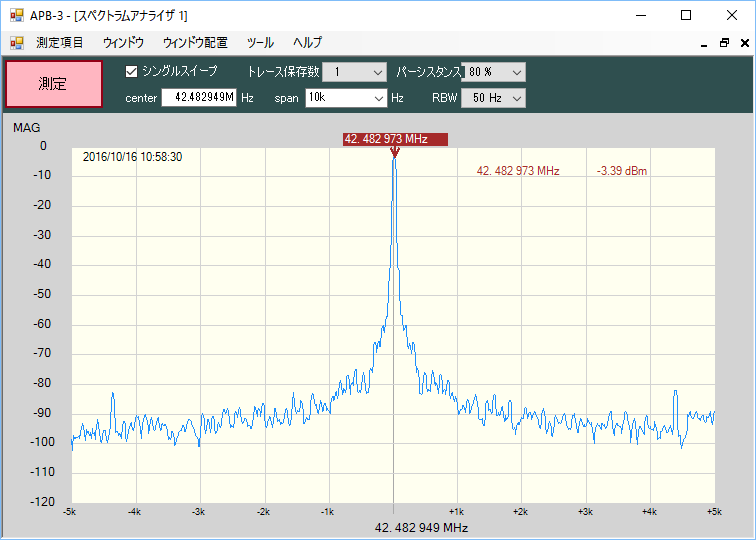

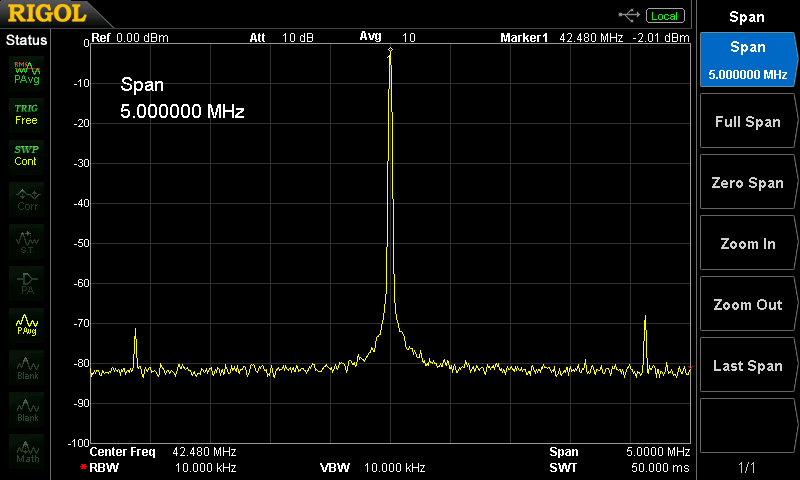

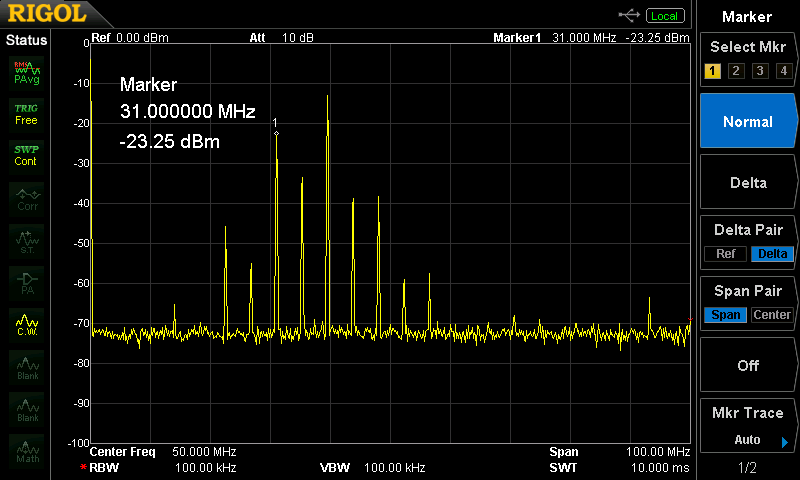

IFは、8MHz帯か9MHz帯を使用する予定です。DDSのプログラムを変更して4.0~4.3MHzまで出力するようにしました。ループフィルタは、適当に決めた状態でも問題なくPLLがロックしました。スペアナでスパンを10KHzと5MHzで見てみましたが、とりあえず問題はなさそうです。受信機で聞いてみると微妙にノイズっぽいものが聞こえますが、ブレッドボードでの環境が影響している可能性もあります。

AD9833は価格の安いDDS-ICなので、高い周波数までの出力はできませんが、PLLのリファレンスとして使用するか、またはミキサーICを使用したプリミックスVFOとしてなら十分に利用可能と思われます。

過去のアナログ・デバイセズDDS-ICの制御プログラムと大きな違いはありませんが、参考までに載せておきます。使いまわしなので、余分なコードがあります。開発はMPLAB X IDEv3.10を使用し、Cコンパイラは、XC8version1.21を使用しています。

プリミックスVFOのテスト

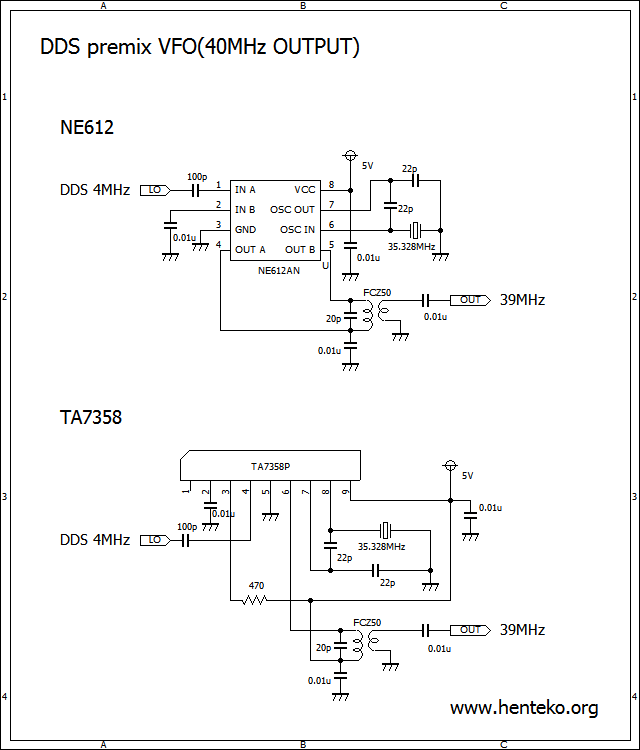

ミキサーICのNE612ANとTA7358APを使用したプリミックスVFOもテストしてみました。両ICとも水晶発振回路が構成できるので、35MHz帯のXtalで発信させて、DDSからの4MHz帯の信号と混合させて39MHz帯の出力を得ます。回路図は以下のとおりです。

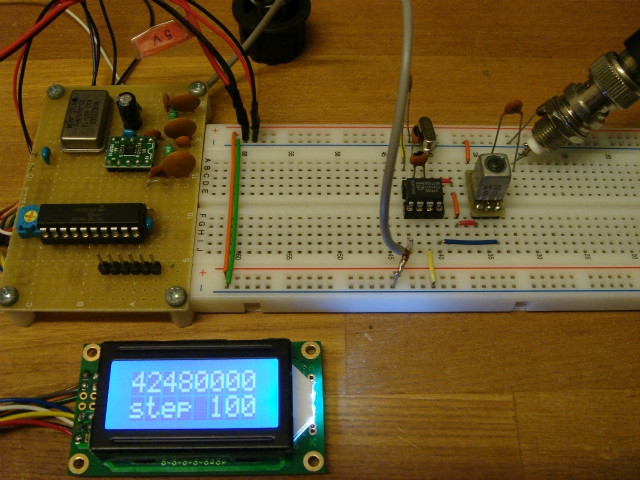

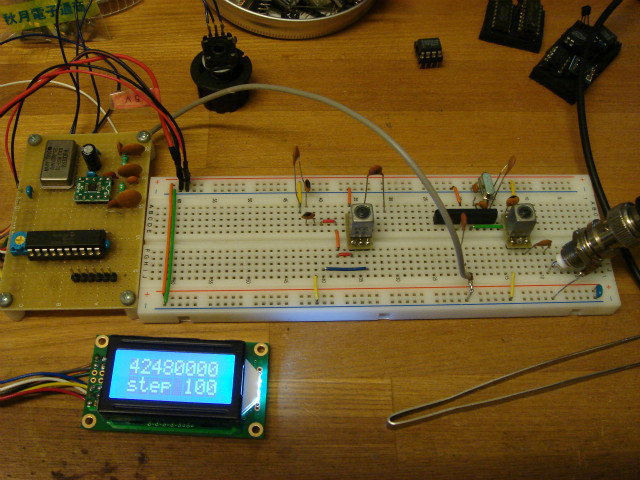

ブレッドボードで実験しました。

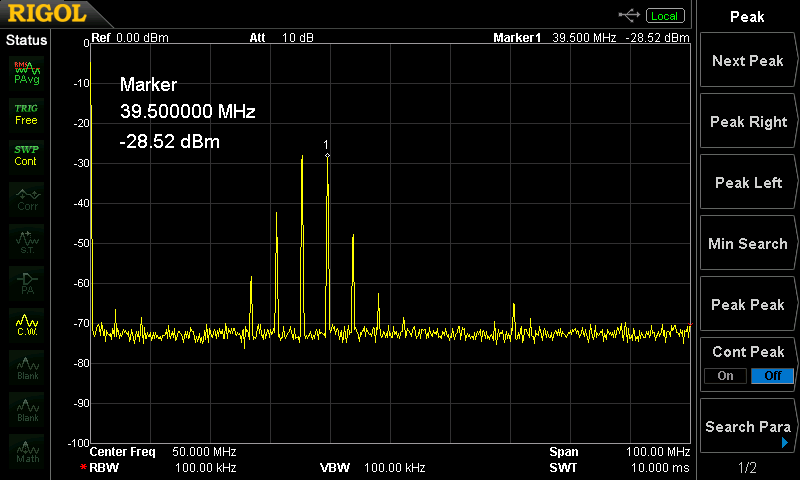

VFOの出力をスペアナで見てみました。左がNE612で右がTA7358です。アッテネータをいくつ入れたか忘れたので出力レベルは適当に見てください。スプリアスの多いこの状況では実際に使用するのは厳しいと思います。基本波から近い(4MHz程度)スプリアスは普通のフィルターでは落としきれません。

ミキサーICを使ったプリミックスVFOは簡単なんですが、使用する周波数をよく考える必要がありそうです。例えばDDSの周波数の2倍程度までの水晶発振信号との混合ならフィルターワークでなんとかなるかもしれません。

1件のピンバック

PLL-VFOを使った50MHzSSBトランシーバーの製作 | henteko.org

コメントは現在停止中です。